# MOS INTEGRATED CIRCUIT $\mu PD784020, 784021$

#### 16/8-BIT SINGLE-CHIP MICROCOMPUTER

The  $\mu$ PD784021 is a product of the  $\mu$ PD784026 sub-series in the 78K/IV series. It contains various peripheral hardware such as RAM, I/O ports, 8-bit resolution A/D and D/A converters, timers, serial interface, and interrupt functions, as well as a high-speed, high-performance CPU.

The  $\mu$ PD784021 is a ROM-less product of the  $\mu$ PD784025 or  $\mu$ PD784026.

The  $\mu$ PD784020 differs from the  $\mu$ PD784021 only in its RAM size: 512 bytes are allocated for the  $\mu$ PD784020, while 2048 bytes are allocated for the  $\mu$ PD784021.

For specific functions and other detailed information, consult the following user's manual. This manual is required reading for design work.

μPD784026 Sub-Series User's Manual, Hardware : U10898E 78K/IV Series User's Manual, Instruction : U10905E

#### **FEATURES**

- 78K/IV series

- ullet Pin-compatible with the  $\mu$ PD78234 sub-series

- Minimum instruction execution time: 160 ns (at 25 MHz)

- Number of I/O ports: 46

- Timer/counters: 16-bit timer/counter × 3 units

16-bit timer × 1 unit

- Serial interface: 3 channels

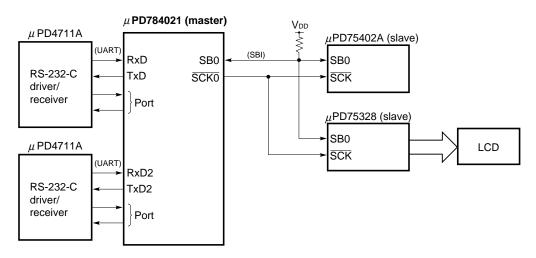

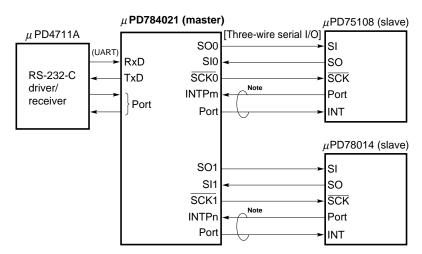

UART/IOE (3-wire serial I/O) :2 channels CSI (3-wire serial I/O, SBI) : 1 channel

PWM outputs: 2Standby function

HALT/STOP/IDLE mode

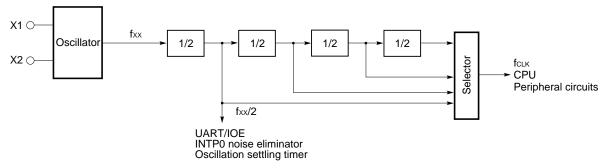

Clock frequency division function

• Watchdog timer: 1 channel

A/D converter : 8-bit resolution × 8 channels

D/A converter : 8-bit resolution × 2 channels

• Supply voltage: VDD = 2.7 to 5.5 V

#### **APPLICATIONS**

LBP, automatic-focusing camera, PPC, printer, electronic typewriter, air conditioner, electronic musical instruments, cellular telephone, etc.

This manual describes the  $\mu$ PD784021 unless otherwise specified.

The information in this document is subject to change without notice.

Document No. U11514EJ1V0DS00 (1st edition) (Previous No. IP-3234)

Date Published July 1996 P

Printed in Japan

#### ORDERING INFORMATION

| Part number |                      | Package                                              | Internal ROM | Internal RAM |  |

|-------------|----------------------|------------------------------------------------------|--------------|--------------|--|

|             |                      |                                                      | (bytes)      | (bytes)      |  |

| *           | μPD784020GC-3B9      | 80-pin plastic QFP (14 × 14 mm)                      | None         | 512          |  |

|             | $\mu$ PD784021GC-3B9 | 80-pin plastic QFP (14 $\times$ 14 mm)               | None         | 2048         |  |

| *           | $\mu$ PD784021GK-BE9 | 80-pin plastic TQFP (fine pitch) (12 $\times$ 12 mm) | None         | 2048         |  |

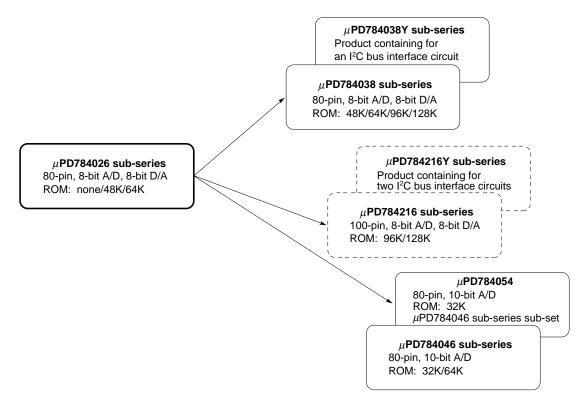

#### **★ 78K/IV SERIES PRODUCT DEVELOPMENT DIAGRAM**

|            | Product under mass produc | tio |

|------------|---------------------------|-----|

|            | Product under development |     |

| <br>!<br>! | Product under planning    |     |

#### **Standard Products Development**

#### **ASSP Development**

µPD784915 sub-series VTR servo, 100-pin, built-in analog amplifier ROM: 48K/62K

#### $\mu$ PD784908 sub-series

100-pin, built-in IEBus<sup>TM</sup> ROM: 96K/128K

#### $\mu$ PD784943 sub-series

80-pin, for CD-ROM

ROM: 56K

# **FUNCTIONS**

| Product                                                         |                      |                                | μ                                                                                                                           | PD784020                                                                                | μPD784021                                                                        |  |

|-----------------------------------------------------------------|----------------------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--|

| Number of basic instructions (mnemonics)                        |                      |                                | 113                                                                                                                         |                                                                                         |                                                                                  |  |

| Ge                                                              | neral-purpos         | e register                     | 8 bits × 16 registers                                                                                                       | s $\times$ 8 banks, or 16 bits $\times$ 8                                               | registers × 8 banks (memory mapping)                                             |  |

| Mir                                                             |                      | ction execution                | 160 ns/320 ns/640                                                                                                           | ns/1280 ns (at 25 MHz)                                                                  |                                                                                  |  |

| Inte                                                            | ernal                | ROM                            | None                                                                                                                        |                                                                                         |                                                                                  |  |

| me                                                              | emory                | RAM                            | 512 bytes                                                                                                                   |                                                                                         | 2048 bytes                                                                       |  |

| Ме                                                              | emory space          |                                | Program and data:                                                                                                           | 1M byte                                                                                 |                                                                                  |  |

| I/O                                                             | ports                | Total                          | 46                                                                                                                          |                                                                                         |                                                                                  |  |

|                                                                 |                      | Input                          | 8                                                                                                                           |                                                                                         |                                                                                  |  |

|                                                                 |                      | Input/output                   | 34                                                                                                                          |                                                                                         |                                                                                  |  |

|                                                                 |                      | Output                         | 4                                                                                                                           |                                                                                         |                                                                                  |  |

|                                                                 | Additional function  | Pins with pull-<br>up resistor | 32                                                                                                                          |                                                                                         |                                                                                  |  |

|                                                                 | pins <sup>Note</sup> | LED direct drive outputs       | 8                                                                                                                           |                                                                                         |                                                                                  |  |

|                                                                 |                      | Transistor direct drive        | 8                                                                                                                           |                                                                                         |                                                                                  |  |

| Re                                                              | al-time outpu        | t ports                        | 4 bits $\times$ 2, or 8 bits                                                                                                | × 1                                                                                     |                                                                                  |  |

| Tin                                                             | ner/counter          |                                | Timer/counter 0:<br>(16 bits)                                                                                               | Timer register $\times$ 1<br>Capture register $\times$ 1<br>Compare register $\times$ 2 | Pulse output capability • Toggle output • PWM/PPG output • One-shot pulse output |  |

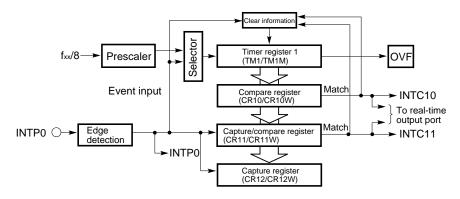

|                                                                 |                      |                                | Timer/counter 1: (8/16 bits)                                                                                                | Timer register × 1 Capture register × 1 Capture/compare register Compare register × 1   | Pulse output capability  ■ Real-time output (4 bits × 2)  × 1                    |  |

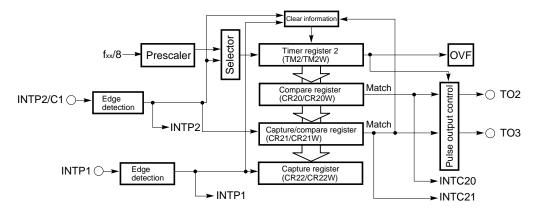

|                                                                 |                      |                                | Timer/counter 2: (8/16 bits)                                                                                                | Timer register × 1 Capture register × 1 Capture/compare register Compare register × 1   | Pulse output capability  • Toggle output  × 1  • PWM/PPG output                  |  |

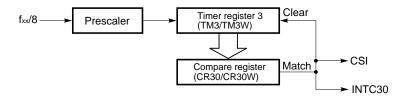

|                                                                 |                      |                                | Timer 3 : (8/16 bits)                                                                                                       | Timer register × 1 Compare register × 1                                                 |                                                                                  |  |

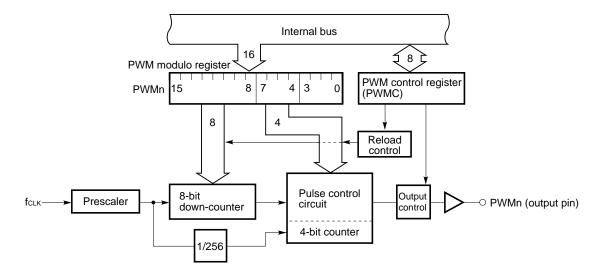

| Р۷                                                              | VM outputs           |                                | 12-bit resolution ×                                                                                                         | 2 channels                                                                              |                                                                                  |  |

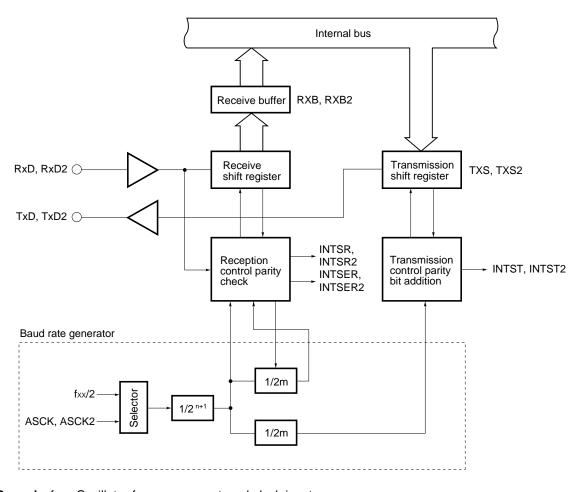

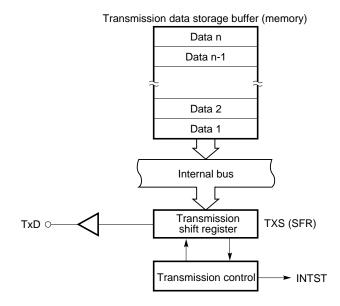

| Se                                                              | rial interface       |                                | UART/IOE (3-wire serial I/O): 2 channels (incorporating baud rate generator) CSI (3-wire serial I/O, SBI): 1 channel        |                                                                                         |                                                                                  |  |

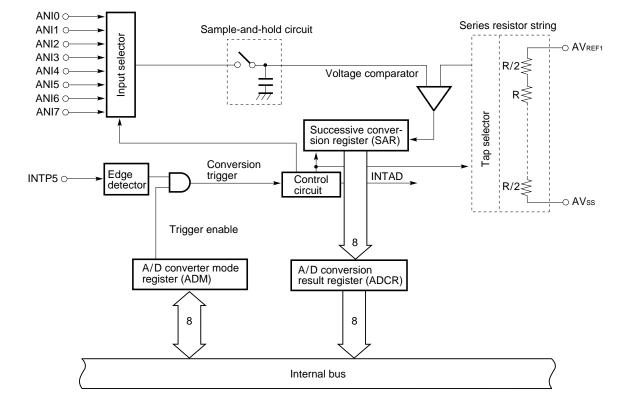

| A/E                                                             | O converter          |                                | 8-bit resolution × 8 channels                                                                                               |                                                                                         |                                                                                  |  |

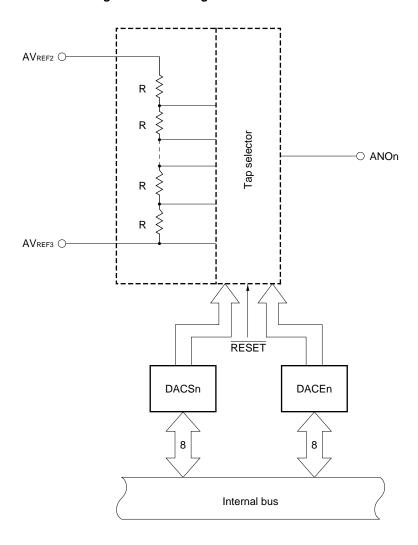

| D/A                                                             | A converter          |                                | 8-bit resolution × 2 channels                                                                                               |                                                                                         |                                                                                  |  |

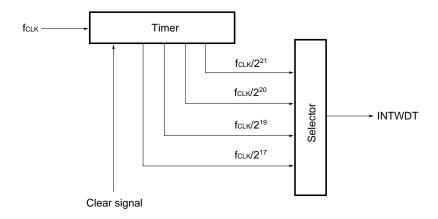

| Wa                                                              | atchdog timer        |                                | 1 channel                                                                                                                   |                                                                                         |                                                                                  |  |

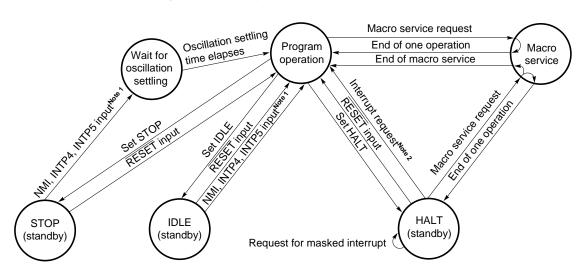

| Standby                                                         |                      |                                | HALT/STOP/IDLE mode                                                                                                         |                                                                                         |                                                                                  |  |

| Interrupt Source 23 (16 internal, 7 external (sampling clock va |                      |                                | iable input: 1)) + BRK instruction                                                                                          |                                                                                         |                                                                                  |  |

| Software<br>Nonmaskable                                         |                      | Software                       | BRK instruction                                                                                                             |                                                                                         |                                                                                  |  |

|                                                                 |                      | 1 internal, 1 external         |                                                                                                                             |                                                                                         |                                                                                  |  |

|                                                                 |                      | Maskable                       | 15 internal, 6 external                                                                                                     |                                                                                         |                                                                                  |  |

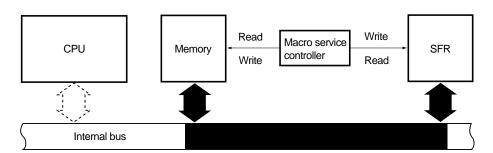

|                                                                 |                      |                                | 4-level programmable priority     3 operation statuses: vectored interrupt, macro service, context switching                |                                                                                         |                                                                                  |  |

| Su                                                              | pply voltage         |                                | V <sub>DD</sub> = 2.7 to 5.5 V                                                                                              |                                                                                         |                                                                                  |  |

| Package                                                         |                      |                                | 80-pin plastic QFP (14 $\times$ 14 mm)<br>80-pin plastic TQFP (fine pitch) (12 $\times$ 12 mm): for the $\mu$ PD784021 only |                                                                                         |                                                                                  |  |

Note Additional function pins are included in the I/O pins.

^

# **CONTENTS**

| 1.                              | . DIFFERENCES BETWEEN $\mu$ PD784026 SUB-SERIES                                                                                                                     |                                                                         |                                                                                                                                                                                                                                         |                                                          |  |  |  |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|--|--|--|

| 2.                              | MAIN DIFFERENCES BETWEEN $\mu$ PD784026 AND $\mu$ PD78234 SUB-SERIES                                                                                                |                                                                         |                                                                                                                                                                                                                                         |                                                          |  |  |  |

| 3. PIN CONFIGURATION (TOP VIEW) |                                                                                                                                                                     |                                                                         |                                                                                                                                                                                                                                         |                                                          |  |  |  |

| 4.                              | SYST                                                                                                                                                                | EM COI                                                                  | NFIGURATION EXAMPLE (PPC)                                                                                                                                                                                                               | 10                                                       |  |  |  |

| 5.                              | BLO                                                                                                                                                                 | CK DIAG                                                                 | BRAM                                                                                                                                                                                                                                    | 11                                                       |  |  |  |

| 6.                              | LIST OF PIN FUNCTIONS       1         6.1 PORT PINS       1         6.2 NON-PORT PINS       1         6.3 I/O CIRCUITS FOR PINS AND HANDLING OF UNUSED PINS       1 |                                                                         |                                                                                                                                                                                                                                         |                                                          |  |  |  |

| 7.                              | CPU<br>7.1<br>7.2                                                                                                                                                   | MEMOF                                                                   | ECTURE                                                                                                                                                                                                                                  | 21<br>21<br>22                                           |  |  |  |

| 8.                              | PERII<br>8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6<br>8.7<br>8.8                                                                                                       | PORTS CLOCK REAL-1 TIMERS PWM O A/D CO D/A CO SERIAL 8.8.1 8.8.2 EDGE I | HARDWARE FUNCTIONS  GENERATOR  GIME OUTPUT PORT  S/COUNTERS  OUTPUT (PWM0, PWM1)  ONVERTER  ONVERTER  INTERFACE  Asynchronous Serial Interface/Three-Wire Serial I/O (UART/IOE)  Synchronous Serial Interface (CSI)  DETECTION FUNCTION | 28<br>29<br>31<br>32<br>34<br>35<br>36<br>37<br>38<br>40 |  |  |  |

| 9.                              | 9.1<br>9.2<br>9.3<br>9.4<br>9.5                                                                                                                                     | INTERF<br>VECTO<br>CONTE<br>MACRO                                       | FUNCTION                                                                                                                                                                                                                                | 43<br>43<br>45<br>46<br>46                               |  |  |  |

| 10. | LOCA   | L BUS INTERFACE                    | 49  |   |

|-----|--------|------------------------------------|-----|---|

|     |        | MEMORY EXPANSION                   | 49  |   |

|     |        | MEMORY SPACE                       | 50  |   |

|     |        | PROGRAMMABLE WAIT                  | 51  |   |

|     |        | PSEUDO-STATIC RAM REFRESH FUNCTION | 51  |   |

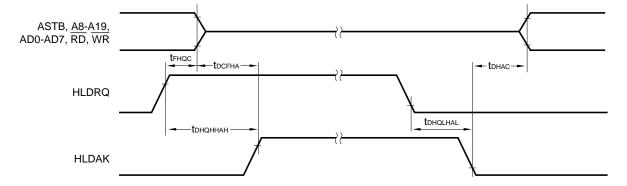

|     | 10.5   | BUS HOLD FUNCTION                  | 51  |   |

| 11. | STANI  | DBY FUNCTION                       | 52  |   |

| 12. | RESE   | Γ FUNCTION                         | 53  |   |

| 13. | INSTR  | UCTION SET                         | 54  |   |

| 14. | ELECT  | TRICAL CHARACTERISTICS             | 59  | * |

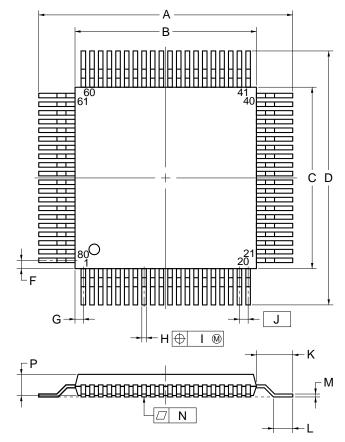

| 15. | PACK   | AGE DRAWINGS                       | 80  |   |

| 16. | RECO   | MMENDED SOLDERING CONDITIONS       | 82  | * |

| AP  | PENDIX | A DEVELOPMENT TOOLS                | 83  |   |

| A D |        | A DELATED DOCUMENTS                | 0.5 |   |

## ★ 1. DIFFERENCES BETWEEN $\mu$ PD784026 SUB-SERIES

The only difference between the  $\mu$ PD784020,  $\mu$ PD784021,  $\mu$ PD784025, and  $\mu$ PD784026 is their capacity of internal memory, port functions, and part of their packages.

The  $\mu$ PD78P4026 is produced by replacing the masked ROM in the  $\mu$ PD784025 or  $\mu$ PD784026 with 64K-byte one-time PROM or EPROM. Table 1-1 shows the differences between these products.

Table 1-1 Differences between the  $\mu$ PD784026 Sub-Series

| Product<br>Item | μPD784020                                                       | μPD784021                                           | μPD784025                                                                        | μPD784026                               | μPD78P4026                               |

|-----------------|-----------------------------------------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------------|-----------------------------------------|------------------------------------------|

| Internal ROM    | None                                                            |                                                     | 48K bytes<br>(masked ROM)                                                        | 64K bytes<br>(masked ROM)               | 64K bytes<br>(one-time PROM<br>or EPROM) |

| Internal RAM    | 512 bytes                                                       | 2048 bytes                                          |                                                                                  |                                         |                                          |

| P40-P47         | Functions only as ar                                            | address/data bus                                    | Can be switched to a general-purpose port or address/data bus, by using software |                                         |                                          |

| P50-P57         | Functions only as ar                                            | address bus                                         | Can be switched to a general-purpose port or address bus in                      |                                         |                                          |

| P60-P63         | Can be switched to a<br>or address bus in un<br>using software  |                                                     | units of 2 bits, by us                                                           | ing software                            |                                          |

| P64, P65        | Functions only as the RD or WR pin                              |                                                     |                                                                                  | or WR pin when the as a general-purpose |                                          |

| Package         | 80-pin plastic QFP 80-pin plastic QFP (14 × 14 mm) (14 × 14 mm) |                                                     | 80-pin plastic QFP (                                                             | 14 × 14 mm)                             | 80-pin plastic QFP (14 × 14 mm)          |

|                 |                                                                 | 80-pin plastic<br>TQFP (fine pitch)<br>(12 × 12 mm) |                                                                                  |                                         | 80-pin ceramic<br>WQFN<br>(14 × 14 mm)   |

# 2. MAIN DIFFERENCES BETWEEN $\mu$ PD784026 AND $\mu$ PD78234 SUB-SERIES

| Series<br>Item   |                       | μPD784026 sub-series                                                                                                                                                                                       | μPD78234 sub-series                                                                                                                                                                                        |  |

|------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Number o         | f basic instructions  | 113                                                                                                                                                                                                        | 65                                                                                                                                                                                                         |  |

| Minimum<br>time  | instruction execution | 160 ns<br>(at 25 MHz)                                                                                                                                                                                      | 333 ns<br>(at 12 MHz)                                                                                                                                                                                      |  |

| Memory s         | pace (program/data)   | 1M byte in total                                                                                                                                                                                           | 64K bytes/1M byte                                                                                                                                                                                          |  |

| Timer/cou        | nter                  | 16-bit timer/counter × 1<br>8/16-bit timer/counter × 2<br>8/16-bit timer × 1                                                                                                                               | 16-bit timer/counter × 1<br>8-bit timer/counter × 2<br>8-bit timer × 1                                                                                                                                     |  |

| Clock out        | out function          | Available                                                                                                                                                                                                  | Unavailable                                                                                                                                                                                                |  |

| Watchdog         | timer                 | Available                                                                                                                                                                                                  | Unavailable                                                                                                                                                                                                |  |

| Serial inte      | rface                 | UART/IOE (3-wire serial I/O) × 2 channels<br>CSI (3-wire serial I/O, SBI) × 1 channel                                                                                                                      | UART $\times$ 1 channel CSI (3-wire serial I/O, SBI) $\times$ 1 channel                                                                                                                                    |  |

| Interrupt        | Context switching     | Available                                                                                                                                                                                                  | Unavailable                                                                                                                                                                                                |  |

|                  | Priority              | 4 levels                                                                                                                                                                                                   | 2 levels                                                                                                                                                                                                   |  |

| Standby f        | unction               | 3 modes (HALT, STOP, IDLE)                                                                                                                                                                                 | 2 modes (HALT, STOP)                                                                                                                                                                                       |  |

| Operation        | clock switching       | Selectable from fxx/2, fxx/4, fxx/8, or fxx/16                                                                                                                                                             | Fixed to fxx/2                                                                                                                                                                                             |  |

| Pin<br>functions | MODE pin              | Unavailable                                                                                                                                                                                                | To specify ROM-less mode (always in the high level for the $\mu$ PD78233 or $\mu$ PD78237)                                                                                                                 |  |

| TEST pin         |                       | Pin for testing the device<br>Low level during ordinary use                                                                                                                                                | Unavailable                                                                                                                                                                                                |  |

| Package          |                       | 80-pin plastic QFP (14 $\times$ 14 mm)<br>80-pin plastic TQFP (fine pitch)<br>(12 $\times$ 12 mm): for the $\mu$ PD784021 only<br>80-pin ceramic WQFN (14 $\times$ 14 mm):<br>for the $\mu$ PD78P4026 only | 80-pin plastic QFP (14 $\times$ 14 mm)<br>94-pin plastic QFP (20 $\times$ 20 mm)<br>84-pin plastic QFJ (1150 $\times$ 1150 mil)<br>94-pin ceramic WQFN (20 $\times$ 20 mm):<br>for the $\mu$ PD78P238 only |  |

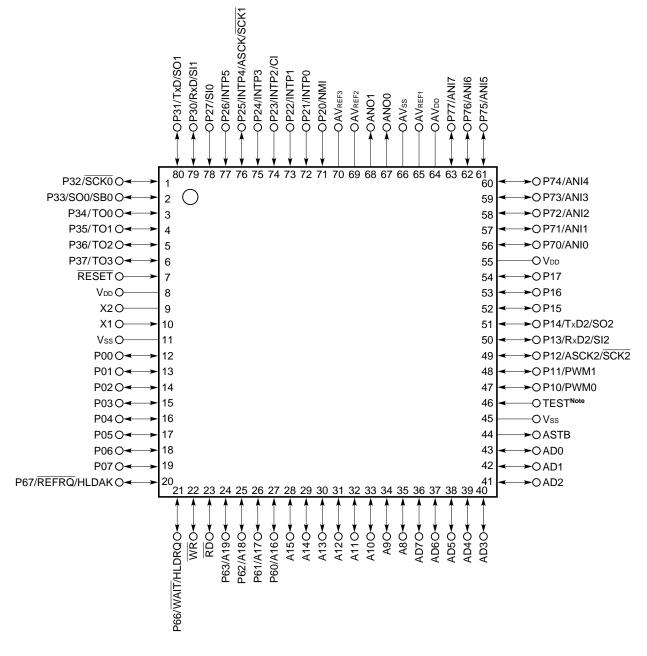

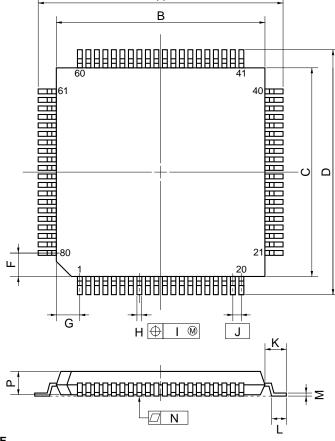

#### 3. PIN CONFIGURATION (TOP VIEW)

- 80-pin plastic QFP (14 × 14 mm)

μPD784020GC-3B9, μPD784021GC-3B9

- 80-pin plastic TQFP (fine pitch) (12 × 12 mm)

- ★ µPD784021GK-BE9

Note Connect the TEST pin to Vss directly.

INTP0-INTP5

AD0-AD7

P00-P07 : Port 0 A8-A19 : Address bus  $\overline{\mathsf{RD}}$ : Read strobe P10-P17 : Port 1 : Port 2  $\overline{\mathsf{WR}}$ P20-P27 : Write strobe WAIT P30-P37 : Port 3 : Wait P60-P63, P66, P67: Port 6 **HLDRQ** : Hold request : Port 7 HLDAK P70-P77 : Hold acknowledge TO0-TO3 : Timer output ASTB : Address strobe REFRQ CI : Clock input : Refresh request RxD, RxD2 : Receive data RESET : Reset : Transmit data TxD, TxD2 X1, X2 : Crystal SCK0-SCK2 : Serial clock ANIO-ANI7 : Analog input ASCK, ASCK2 : Asynchronous serial clock ANO0, ANO1 : Analog output SI0-SI2 : Serial input AVREF1-AVREF3: Reference voltage SO0-SO2 : Serial output AVDD : Analog power supply SB0 : Serial bus AVss : Analog ground PWM0, PWM1 : Pulse width modulation output  $V_{\text{DD}}$ : Power supply NMI : Non-maskable interrupt Vss : Ground

: Interrupt from peripherals

: Address/data bus

TEST

: Test

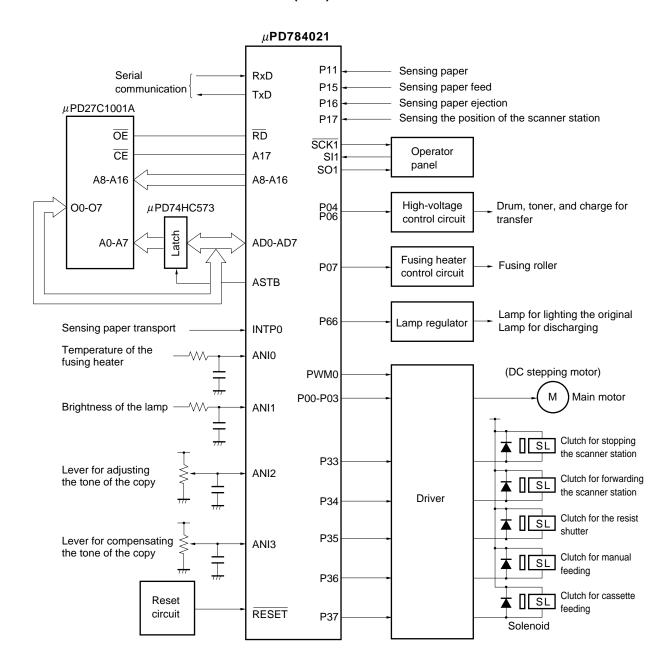

#### 4. SYSTEM CONFIGURATION EXAMPLE (PPC)

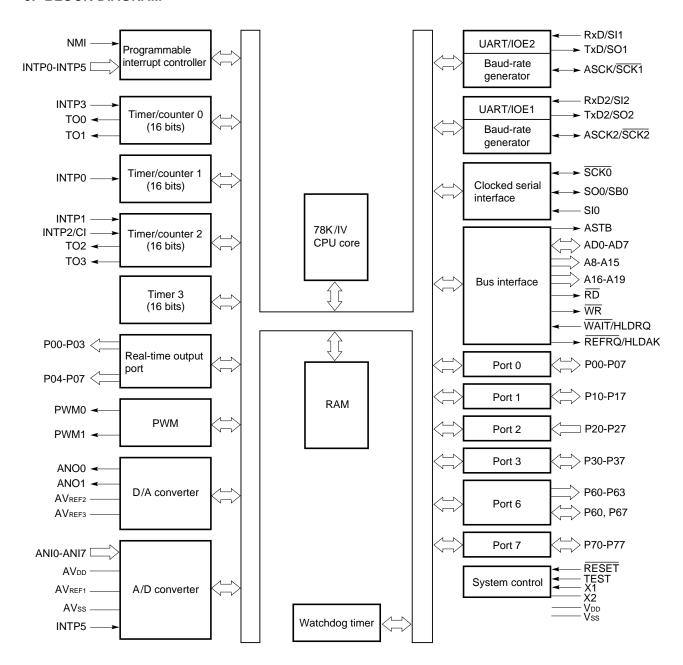

#### 5. BLOCK DIAGRAM

Remark The internal ROM or RAM capacity differs for each product.

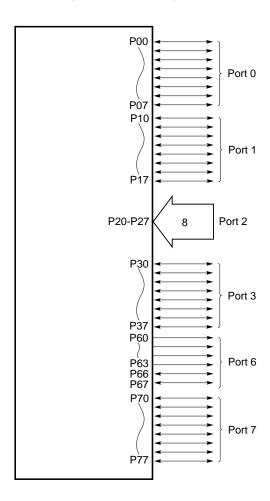

# 6. LIST OF PIN FUNCTIONS

# 6.1 PORT PINS

| Pin     | I/O   | Dual-function   | Function                                                                                                                              |

|---------|-------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------|

| P00-P07 | I/O   | _               | Port 0 (P0):                                                                                                                          |

|         |       |                 | 8-bit I/O port                                                                                                                        |

|         |       |                 | • Functions as a real-time output port (4 bits × 2).                                                                                  |

|         |       |                 | Inputs and outputs can be specified bit by bit.                                                                                       |

|         |       |                 | The use of the pull-up resistors can be specified by software for the pins in the input mode together.                                |

|         |       |                 | Can drive a transistor.                                                                                                               |

| P10     | I/O   | PWM0            | Port 1 (P1):                                                                                                                          |

| P11     |       | PWM1            | 8-bit I/O port                                                                                                                        |

| P12     |       | ASCK2/SCK2      | Inputs and outputs can be specified bit by bit.                                                                                       |

| P13     |       | RxD2/SI2        | The use of the pull-up resistors can be specified by software for the pins                                                            |

| P14     |       | TxD2/SO2        | in the input mode together.                                                                                                           |

| P15-P17 |       | _               | Can drive LED.                                                                                                                        |

| P20     | Input | NMI             | Port 2 (P2):                                                                                                                          |

| P21     |       | INTP0           | 8-bit input-only port                                                                                                                 |

| P22     | 7     | INTP1           | P20 does not function as a general-purpose port (nonmaskable inter-                                                                   |

| P23     |       | INTP2/CI        | rupt). However, the input level can be checked by an interrupt service                                                                |

| P24     | 7     | INTP3           | routine.                                                                                                                              |

| P25     |       | INTP4/ASCK/SCK1 | The use of the pull-up resistors can be specified by software for pins     P22 to P27 (in units of 6 bits).                           |

| P26     |       | INTP5           | • The P25/INTP4/ASCK/SCK1 pin functions as the SCK1 output pin by                                                                     |

| P27     |       | SIO             | CSIM1.                                                                                                                                |

| P30     | I/O   | RxD/SI1         | Port 3 (P3):                                                                                                                          |

| P31     | 7     | TxD/SO1         | 8-bit I/O port                                                                                                                        |

| P32     |       | SCK0            | Inputs and outputs can be specified bit by bit.                                                                                       |

| P33     |       | SO0/SB0         | The use of the pull-up resistors can be specified by software for the pins                                                            |

| P34-P37 |       | TO0-TO3         | in the input mode together.                                                                                                           |

| P60-P63 | I/O   | A16-A19         | Port 6 (P6):                                                                                                                          |

| P66     |       | WAIT/HLDRQ      | <ul> <li>P60 to P63 are an output-only port.</li> <li>Inputs and outputs can be specified bit by bit for pins P66 and P67.</li> </ul> |

| P67     |       | REFRQ/HLDAK     | The use of the pull-up resistors can be specified by software for the pins in the input mode together.                                |

| P70-P77 | I/O   | ANI0-ANI7       | Port 7 (P7):                                                                                                                          |

|         |       |                 | 8-bit I/O port                                                                                                                        |

|         |       |                 | Inputs and outputs can be specified bit by bit.                                                                                       |

# 6.2 NON-PORT PINS (1/2)

| Pin     | I/O    | Dual-function  | Function                                     |                                                                                        |  |

|---------|--------|----------------|----------------------------------------------|----------------------------------------------------------------------------------------|--|

| TO0-TO3 | Output | P34-P37        | Timer output                                 |                                                                                        |  |

| CI      | Input  | P23/INTP2      | Input of a count clock for timer/counter 2   |                                                                                        |  |

| RxD     | Input  | P30/SI1        | Serial data input (UAF                       | RT0)                                                                                   |  |

| RxD2    |        | P13/SI2        | Serial data input (UAF                       | RT2)                                                                                   |  |

| TxD     | Output | P31/SO1        | Serial data output (UA                       | ARTO)                                                                                  |  |

| TxD2    |        | P14/SO2        | Serial data output (UA                       | ART2)                                                                                  |  |

| ASCK    | Input  | P25/INTP4/SCK1 | Baud rate clock input                        | (UARTO)                                                                                |  |

| ASCK2   |        | P12/SCK2       | Baud rate clock input                        | (UART2)                                                                                |  |

| SB0     | I/O    | P33/SO0        | Serial data I/O (SBI)                        |                                                                                        |  |

| SI0     | Input  | P27            | Serial data input (3-w                       | ire serial I/O0)                                                                       |  |

| SI1     |        | P30/RxD        | Serial data input (3-w                       | ire serial I/O1)                                                                       |  |

| SI2     |        | P13/RxD2       | Serial data input (3-w                       | ire serial I/O2)                                                                       |  |

| SO0     | Output | P33/SB0        | Serial data output (3-                       | wire serial I/O0)                                                                      |  |

| SO1     |        | P31/TxD        | Serial data output (3-v                      | wire serial I/O1)                                                                      |  |

| SO2     |        | P14/TxD2       | Serial data output (3-v                      | wire serial I/O2)                                                                      |  |

| SCK0    | I/O    | P32            | Serial clock I/O (3-wir                      | e serial I/O0, SBI)                                                                    |  |

| SCK1    |        | P25/INTP4/ASCK | Serial clock I/O (3-wir                      | re serial I/O1)                                                                        |  |

| SCK2    |        | P12/ASCK2      | Serial clock I/O (3-wir                      | re serial I/O2)                                                                        |  |

| NMI     | Input  | P20            | External interrupt request                   | _                                                                                      |  |

| INTP0   |        | P21            |                                              | Input of a count clock for timer/counter 1     Capture/trigger signal for CR11 or CR12 |  |

| INTP1   |        | P22            |                                              | Input of a count clock for timer/counter 2     Capture/trigger signal for CR22         |  |

| INTP2   |        | P23/CI         |                                              | Input of a count clock for timer/counter 2     Capture/trigger signal for CR21         |  |

| INTP3   |        | P24            |                                              | Input of a count clock for timer/counter 0     Capture/trigger signal for CR02         |  |

| INTP4   |        | P25/ASCK/SCK1  | -                                            | _                                                                                      |  |

| INTP5   |        | P26            | -                                            | Input of a conversion start trigger for A/D converter                                  |  |

| AD0-AD7 | I/O    | _              | Time multiplexing add                        | dress/data bus (for connecting external memory)                                        |  |

| A8-A15  | Output | _              | High-order address bu                        | us (for connecting external memory)                                                    |  |

| A16-A19 | Output | P60-P63        | High-order address bus d                     | luring address expansion (for connecting external memory)                              |  |

| RD      | Output | _              | Strobe signal output f                       | or reading the contents of external memory                                             |  |

| WR      | Output | _              | Strobe signal output f                       | or writing on external memory                                                          |  |

| WAIT    | Input  | P66/HLDRQ      | Wait signal insertion                        |                                                                                        |  |

| REFRQ   | Output | P67/HLDAK      | Refresh pulse output                         | to external pseudo static memory                                                       |  |

| HLDRQ   | Input  | P66/WAIT       | Input of bus hold request                    |                                                                                        |  |

| HLDAK   | Output | P67/REFRQ      | Output of bus hold res                       | sponse                                                                                 |  |

| ASTB    | Output | _              | Latch timing output of connecting external m | time multiplexing address (A0-A7) (for nemory)                                         |  |

# 6.2 NON-PORT PINS (2/2)

| Pin                | I/O    | Dual-function | Function                                                              |  |

|--------------------|--------|---------------|-----------------------------------------------------------------------|--|

| RESET              | Input  | _             | Chip reset                                                            |  |

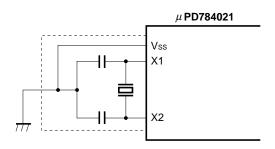

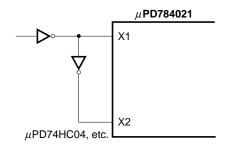

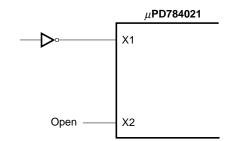

| X1                 | Input  | _             | Crystal input for system clock oscillation (A clock pulse can also be |  |

| X2                 | _      |               | input to the X1 pin.)                                                 |  |

| ANI0-ANI7          | Input  | P70-P77       | Analog voltage inputs for the A/D converter                           |  |

| ANO0, ANO1         | Output | _             | Analog voltage inputs for the D/A converter                           |  |

| AV <sub>REF1</sub> | _      | _             | Application of A/D converter reference voltage                        |  |

| AVREF2, AVREF3     |        |               | Application of D/A converter reference voltage                        |  |

| AV <sub>DD</sub>   |        |               | Positive power supply for the A/D converter                           |  |

| AVss               |        |               | Ground for the A/D converter                                          |  |

| V <sub>DD</sub>    |        |               | Positive power supply                                                 |  |

| Vss                |        |               | Ground                                                                |  |

| TEST               |        |               | Directly connect to Vss. (The TEST pin is for the IC test.)           |  |

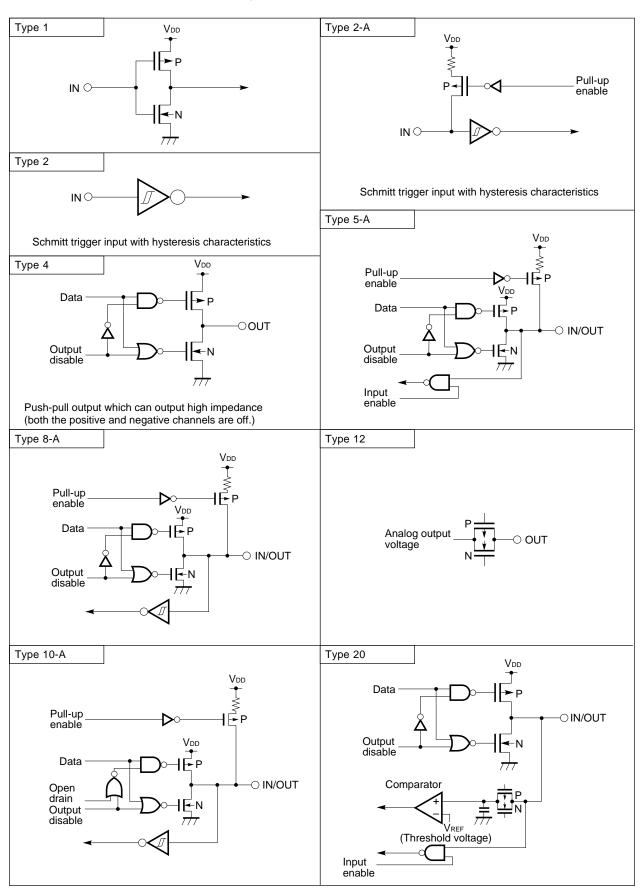

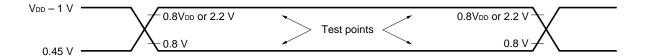

#### 6.3 I/O CIRCUITS FOR PINS AND HANDLING OF UNUSED PINS

Table 6-1 describes the types of I/O circuits for pins and the handling of unused pins.

Fig. 6-1 shows the configuration of these various types of I/O circuits.

Table 6-1 Types of I/O Circuits for Pins and Handling of Unused Pins (1/2)

| Pin                 | I/O circuit type | I/O        | Recommended connection method for unused pins         |

|---------------------|------------------|------------|-------------------------------------------------------|

| P00-P07             | 5-A              | I/O        | Input state : To be connected to V <sub>DD</sub>      |

| P10/PWM0            |                  |            | Output state: To be left open                         |

| P11/PWM1            |                  |            |                                                       |

| P12/ASCK2/SCK2      | 8-A              |            |                                                       |

| P13/RxD2/SI2        | 5-A              |            |                                                       |

| P14/TxD2/SO2        |                  |            |                                                       |

| P15-P17             |                  |            |                                                       |

| P20/NMI             | 2                | Input      | To be connected to V <sub>DD</sub> or V <sub>SS</sub> |

| P21/INTP0           |                  |            |                                                       |

| P22/INTP1           | 2-A              |            | To be connected to VDD                                |

| P23/INTP2/CI        |                  |            |                                                       |

| P24/INTP3           |                  |            |                                                       |

| P25/INTP4/ASCK/SCK1 | 8-A              | I/O        | Input state : To be connected to VDD                  |

|                     |                  |            | Output state: To be left open                         |

| P26/INTP5           | 2-A              | Input      | To be connected to V <sub>DD</sub>                    |

| P27/SI0             |                  |            |                                                       |

| P30/RxD/SI1         | 5-A              | I/O        | Input state : To be connected to V <sub>DD</sub>      |

| P31/TxD/SO1         |                  |            | Output state: To be left open                         |

| P32/SCK0            | 8-A              |            |                                                       |

| P33/SO0/SB0         | 10-A             |            |                                                       |

| P34/TO0-P37/TO3     | 5-A              |            |                                                       |

| AD0-AD7             |                  |            |                                                       |

| A8-A15              |                  | OutputNote | To be left open                                       |

| P60/A16-P63/A19     |                  |            |                                                       |

| RD                  |                  |            |                                                       |

| WR                  |                  |            |                                                       |

| P66/WAIT/HLDRQ      | ]                | I/O        | Input state : To be connected to VDD                  |

| P67/REFRQ/HLDAK     |                  |            | Output state: To be left open                         |

| P70/ANI0-P77/ANI7   | 20               |            | Input state : To be connected to VDD or VSS           |

|                     |                  |            | Output state: To be left open                         |

| ANO0, ANO1          | 12               | Output     | To be left open                                       |

| ASTB                | 4                |            |                                                       |

Note These pins function as output-only pins depending on the internal circuit, though their I/O type is 5-A.

Table 6-1 Types of I/O Circuits for Pins and Handling of Unused Pins (2/2)

| Pin              | I/O circuit type | I/O   | Recommended connection method for unused pins |

|------------------|------------------|-------|-----------------------------------------------|

| RESET            | 2                | Input | _                                             |

| TEST             | 1                |       | To be connected to Vss directly               |

| AVREF1-AVREF3    | _                |       | To be connected to Vss                        |

| AVss             |                  |       |                                               |

| AV <sub>DD</sub> |                  |       | To be connected to V <sub>DD</sub>            |

Caution When the I/O mode of an I/O dual-function pin is unpredictable, connect the pin to V<sub>DD</sub> through a resistor of 10 to 100 kilohms (particularly when the voltage of the reset input pin becomes higher than that of the low level input at power-on or when I/O is switched by software).

**Remark** Since type numbers are consistent in the 78K series, those numbers are not always serial in each product. (Some circuits are not included.)

Fig. 6-1 I/O Circuits for Pins

#### 7. CPU ARCHITECTURE

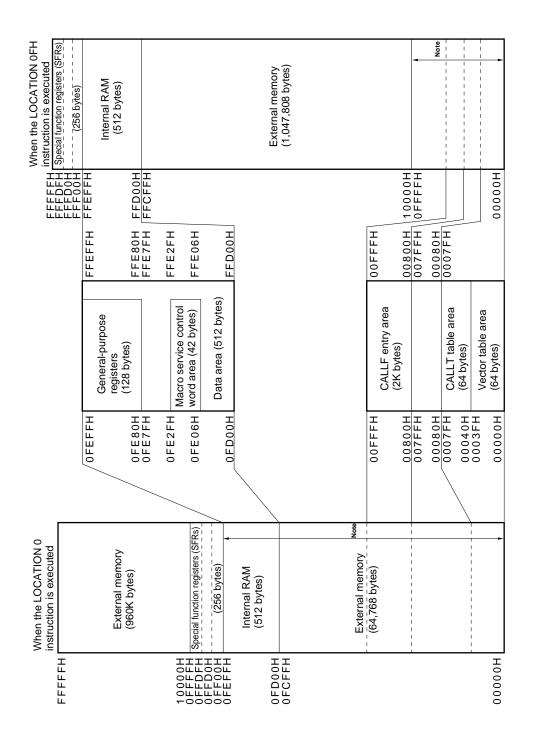

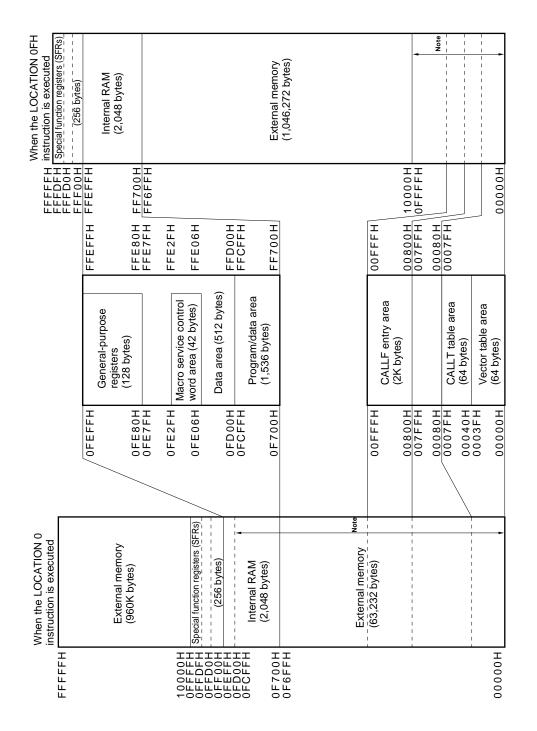

#### 7.1 MEMORY SPACE

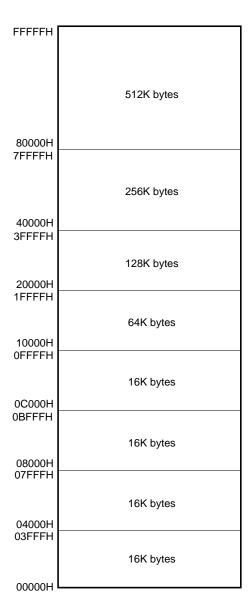

A 1M-byte memory space can be accessed. By using a LOCATION instruction, the mode for mapping internal data areas (special function registers and internal RAM) can be selected. A LOCATION instruction must always be executed after a reset, and can be used only once.

#### (1) When the LOCATION 0 instruction is executed

Internal data areas are mapped to 0FD00H-0FFFFH for the  $\mu$ PD784020 and 0F700H-0FFFFH for the  $\mu$ PD784021.

## (2) When the LOCATION 0FH instruction is executed

Internal data areas are mapped to FFD00H-FFFFFH for the  $\mu$ PD784020 and FF700H-FFFFFH for the  $\mu$ PD784021.

Fig. 7-1 μPD784020 Memory Map★

Note Base area, or entry area based on a reset or interrupt. Internal RAM is excluded in the case of a reset.

Fig. 7-2 µPD784021 Memory Map

Base area, or entry area based on a reset or interrupt. Internal RAM is excluded in the case of a reset. Note

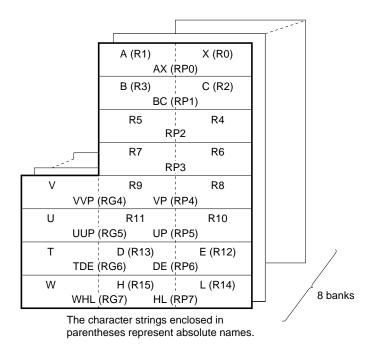

#### 7.2 CPU REGISTERS

#### 7.2.1 General-Purpose Registers

A set of general-purpose registers consists of sixteen general-purpose 8-bit registers. Two 8-bit general-purpose registers can be combined to form a 16-bit general-purpose register. Moreover, four 16-bit general-purpose registers, when combined with an 8-bit register for address extension, can be used as 24-bit address specification registers.

Eight banks of this register set are provided. The user can switch between banks by software or the context switching function.

General-purpose registers other than the V, U, T, and W registers used for address extension are mapped onto internal RAM.

Fig. 7-3 General-Purpose Register Format

Caution By setting the RSS bit of PSW to 1, R4, R5, R6, R7, RP2, and RP3 can be used as the X, A, C, B, AX, and BC registers, respectively. However, this function must be used only when using programs for the 78K/III series.

#### 7.2.2 Control Registers

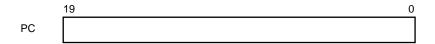

#### (1) Program counter (PC)

This register is a 20-bit program counter. The program counter is automatically updated by program execution.

Fig. 7-4 Format of Program Counter (PC)

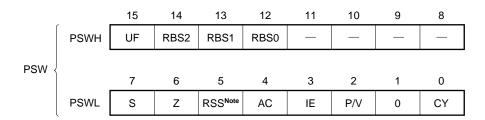

## (2) Program Status Word (PSW)

This register holds the CPU state. The program status word is automatically updated by program execution.

Fig. 7-5 Format of Program Status Word (PSW)

**Note** This flag is used to maintain compatibility with the 78K/III series. This flag must be set to 0 when programs for the 78K/III series are being used.

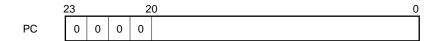

#### (3) Stack pointer (SP)

This register is a 24-bit pointer for holding the start address of the stack. The high-order 4 bits must be set to 0.

Fig. 7-6 Format of Stack Pointer (SP)

#### 7.2.3 Special Function Registers (SFRs)

The special function registers are registers with special functions such as mode registers and control registers for built-in peripheral hardware. The special function registers are mapped onto the 256-byte space between 0FF00H and 0FFFFHNote.

**Note** Applicable when the LOCATION 0 instruction is executed. FFF00H-FFFFFH when the LOCATION 0FH instruction is executed.

Caution Never attempt to access addresses in this area where no SFR is allocated. Otherwise, the  $\mu$ PD784021 may be placed in the deadlock state. The deadlock state can be cleared only by a reset

Table 7-1 lists the special function registers (SFRs). The titles of the table columns are explained below.

| Abbreviation       | Symbol used to represent a built-in SFR. The abbreviations listed in the table are      |

|--------------------|-----------------------------------------------------------------------------------------|

|                    | reserved words for the NEC assembler (RA78K4). The C compiler (CC78K4) allows           |

|                    | the abbreviations to be used as sfr variables of bit type with the #pragma sfr command. |

| • R/W              | Indicates whether each SFR allows read and/or write operations.                         |

|                    | R/W: Allows both read and write operations.                                             |

|                    | R : Allows read operations only.                                                        |

|                    | W : Allows write operations only.                                                       |

| Manipulatable bits | Indicates the maximum number of bits that can be manipulated whenever an SFR is         |

|                    | manipulated. An SFR that supports 16-bit manipulation can be described in the sfr       |

|                    | operand. For address specification, an even-numbered address must be speci-             |

|                    | fied.                                                                                   |

|                    | An SFR that supports 1-bit manipulation can be described in a bit manipulation          |

|                    | instruction.                                                                            |

| When reset         | Indicates the state of each register when RESET is applied.                             |

Table 7-1 Special Function Registers (SFRs) (1/4)

| AddressNote  | Special function register (SFR) name   |                          | Abbreviation |       | R/W     | Manipulatable bits |        |         | When reset  |

|--------------|----------------------------------------|--------------------------|--------------|-------|---------|--------------------|--------|---------|-------------|

| Addressivete | Special function re                    | gister (SFK) flame       | Approviation |       | IX/ V V | 1 bit              | 8 bits | 16 bits | WHICH TOSEL |

| 0FF00H       | Port 0                                 |                          |              |       | R/W     | •                  | •      | -       | Undefined   |

| 0FF01H       | Port 1                                 |                          |              |       |         | •                  | •      | -       |             |

| 0FF02H       | Port 2                                 |                          | P2           |       | R       | •                  | •      | -       |             |

| 0FF03H       | Port 3                                 |                          | P3           |       | R/W     | •                  | •      | _       |             |

| 0FF06H       | Port 6                                 |                          | P6           |       |         | •                  | •      | _       | 00H         |

| 0FF07H       | Port 7                                 |                          | P7           |       |         | •                  | •      | _       | Undefined   |

| 0FF0EH       |                                        | Port 0 buffer register L | P0L          |       |         | •                  | •      | _       |             |

| 0FF0FH       | Port 0 buffer register H               |                          | РОН          |       |         | •                  | •      | _       |             |

| 0FF10H       | Compare register (times                | /counter 0)              | CR00         |       |         | _                  | _      | •       |             |

| 0FF12H       | Capture/compare regist                 | er (timer/counter 0)     | CR01         |       |         | _                  | _      | •       |             |

| 0FF14H       | Compare register L (tim                | er/counter 1)            | CR10         | CR10W |         | _                  | •      | •       |             |

| 0FF15H       | Compare register H (tim                | ner/counter 1)           | _            |       |         | _                  | _      |         |             |

| 0FF16H       | Capture/compare regist                 | er L (timer/counter 1)   | CR11         | CR11W |         | _                  | •      | •       |             |

| 0FF17H       | Capture/compare regist                 | er H (timer/counter 1)   | -            |       |         | -                  | -      |         |             |

| 0FF18H       | Compare register L (tim                | er/counter 2)            | CR20         | CR20W |         | _                  | •      | •       |             |

| 0FF19H       | Compare register H (tim                | ner/counter 2)           | _            |       |         | _                  | -      |         |             |

| 0FF1AH       | Capture/compare regist                 | er L (timer/counter 2)   | CR21         | CR21W |         | _                  | •      | •       |             |

| 0FF1BH       | Capture/compare regist                 | er H (timer/counter 2)   | _            |       |         | _                  | _      |         |             |

| 0FF1CH       | Compare register L (tim                | er 3)                    | CR30         | CR30W |         | _                  | •      | •       |             |

| 0FF1DH       | Compare register H (tim                | ner 3)                   | _            |       |         | _                  | _      |         |             |

| 0FF20H       | Port 0 mode register                   |                          | РМ0          |       |         | •                  | •      | -       | FFH         |

| 0FF21H       | Port 1 mode register                   |                          | PM1          |       |         | •                  | •      | -       |             |

| 0FF23H       | Port 3 mode register                   |                          | РМ3          |       |         | •                  | •      | _       |             |

| 0FF26H       | Port 6 mode register                   |                          |              |       |         | •                  | •      | -       |             |

| 0FF27H       | Port 7 mode register                   |                          |              |       |         | •                  | •      | _       |             |

| 0FF2EH       | Real-time output port control register |                          |              |       |         | •                  | •      | -       | 00H         |

| 0FF30H       | Capture/compare control register 0     |                          |              |       |         | _                  | •      | -       | 10H         |

| 0FF31H       | Timer output control register          |                          |              |       |         | •                  | •      | _       | 00H         |

| 0FF32H       | Capture/compare contro                 | ol register 1            | CRC1         |       |         | _                  | •      | _       |             |

| 0FF33H       | Capture/compare contro                 | ol register 2            | CRC2         |       |         | _                  | •      | _       | 10H         |

**Note** Applicable when the LOCATION 0 instruction is executed. When the LOCATION 0FH instruction is executed, F0000H is added to each address.

Table 7-1 Special Function Registers (SFRs) (2/4)

| AddressNote | Special function register (SED) name       |                  |            | D/M | Manipulatable bits |        |         | When react |

|-------------|--------------------------------------------|------------------|------------|-----|--------------------|--------|---------|------------|

| Addressive  | Special function register (SFR) name       | Abbre            | eviation   | R/W | 1 bit              | 8 bits | 16 bits | When reset |

| 0FF36H      | Capture register (timer/counter 0)         | CR02             | CR02       |     | -                  | _      | •       | 0000H      |

| 0FF38H      | Capture register L (timer/counter 1)       | CR12             | CR12 CR12W |     | -                  | •      | •       |            |

| 0FF39H      | Capture register H (timer/counter 1)       | _                |            |     | _                  | -      |         |            |

| 0FF3AH      | Capture register L (timer/counter 2)       | CR22             | CR22W      |     | _                  | •      | •       |            |

| 0FF3BH      | Capture register H (timer/counter 2)       | _                |            |     | _                  | _      |         |            |

| 0FF41H      | Port 1 mode control register               | PMC1             | •          | R/W | •                  | •      | -       | 00H        |

| 0FF43H      | Port 3 mode control register               | РМСЗ             | 1          |     | •                  | •      | -       |            |

| 0FF4EH      | Register for optional pull-up resistor     | PUO              |            |     | •                  | •      | -       |            |

| 0FF50H      | Timer register 0                           | TM0              |            | R   | -                  | _      | •       | 0000H      |

| 0FF51H      |                                            |                  |            |     | _                  | -      |         |            |

| 0FF52H      | Timer register 1                           | TM1              | TM1W       |     | _                  | •      | •       |            |

| 0FF53H      |                                            | _                |            |     | _                  | -      |         |            |

| 0FF54H      | Timer register 2                           | TM2              | TM2W       |     | _                  | •      | •       |            |

| 0FF55H      |                                            | _                |            |     | _                  | _      |         |            |

| 0FF56H      | Timer register 3                           | TM3              | TM3W       |     | _                  | •      | •       |            |

| 0FF57H      |                                            | _                |            |     | _                  | _      |         |            |

| 0FF5CH      | Prescaler mode register 0                  | PRMO             |            | R/W | -                  | •      | _       | 11H        |

| 0FF5DH      | Timer control register 0                   | TMC0             |            |     | •                  | •      | _       | 00H        |

| 0FF5EH      | Prescaler mode register 1                  | PRM1             |            |     | _                  | •      | -       | 11H        |

| 0FF5FH      | Timer control register 1                   | TMC1             |            |     | •                  | •      | _       | 00H        |

| 0FF60H      | D/A conversion value setting register 0    | DACS             | 0          |     | _                  | •      | -       |            |

| 0FF61H      | D/A conversion value setting register 1    | DACS             | 1          |     | -                  | •      | -       |            |

| 0FF62H      | D/A converter mode register                | DAM              |            |     | •                  | •      | -       | 03H        |

| 0FF68H      | A/D converter mode register                | ADM              |            |     | •                  | •      | _       | 00H        |

| 0FF6AH      | A/D conversion result register             | ADCR             |            | R   | _                  | •      | _       | Undefined  |

| 0FF70H      | PWM control register                       | PWM              | PWMC       |     | •                  | •      | _       | 05H        |

| 0FF71H      | PWM prescaler register                     | PWPF             | PWPR       |     | _                  | •      | _       | 00H        |

| 0FF72H      | PWM modulo register 0                      | PWM0             |            |     | _                  |        | •       | Undefined  |

| 0FF74H      | PWM modulo register 1                      | PWM <sup>2</sup> | PWM1       |     | _                  | _      | •       |            |

| 0FF7DH      | One-shot pulse output control register     | OSPC             |            |     | •                  | •      | _       | 00H        |

| 0FF80H      | Serial bus interface control register      | SBIC             | SBIC       |     | •                  | •      | _       |            |

| 0FF82H      | Synchronous serial interface mode register | CSIM             |            |     | •                  | •      | _       |            |

**Note** Applicable when the LOCATION 0 instruction is executed. When the LOCATION 0FH instruction is executed, F0000H is added to each address.

Table 7-1 Special Function Registers (SFRs) (3/4)

| AddressNote 1 | Special function register (SFR) name            | Abbreviation | R/W   | Manipulatable bits |         |         | When reset    |

|---------------|-------------------------------------------------|--------------|-------|--------------------|---------|---------|---------------|

| Addressives i | Special function register (31 K) fiame          | Abbieviation | IX/VV | 1 bit              | 8 bits  | 16 bits | vviicii ieset |

| 0FF84H        | Synchronous serial interface mode register 1    | CSIM1        | R/W   | •                  | •       | -       | 00H           |

| 0FF85H        | Synchronous serial interface mode register 2    | CSIM2        |       | •                  | •       | -       |               |

| 0FF86H        | Serial shift register                           | SIO          |       | -                  | •       | -       |               |

| 0FF88H        | Asynchronous serial interface mode register     | ASIM         |       | •                  | •       | -       |               |

| 0FF89H        | Asynchronous serial interface mode register 2   | ASIM2        |       | •                  | •       | -       |               |

| 0FF8AH        | Asynchronous serial interface status register   | ASIS         | R     | •                  | •       | _       |               |

| 0FF8BH        | Asynchronous serial interface status register 2 | ASIS2        |       | •                  | •       | _       |               |

| 0FF8CH        | Serial receive buffer: UART0                    | RXB          |       | -                  | •       | _       | Undefined     |

|               | Serial transmission shift register: UART0       | TXS          | W     | -                  | •       | _       |               |

|               | Serial shift register: IOE1                     | SIO1         | R/W   | -                  | •       | _       |               |

| 0FF8DH        | Serial receive buffer: UART2                    | RXB2         | R     | -                  | •       | _       | •             |

|               | Serial transmission shift register: UART2       | TXS2         | W     | -                  | •       | _       |               |

|               | Serial shift register: IOE2                     | SIO2         | R/W   | -                  | •       | _       |               |

| 0FF90H        | Baud rate generator control register            | BRGC         |       | 1                  | •       | _       | 00H           |

| 0FF91H        | Baud rate generator control register 2          | BRGC2        |       | -                  | •       | _       |               |

| 0FFA0H        | External interrupt mode register 0              | INTM0        |       | •                  | •       | _       |               |

| 0FFA1H        | External interrupt mode register 1              | INTM1        |       | •                  | •       | _       |               |

| 0FFA4H        | Sampling clock selection register               | SCS0         |       | 1                  | •       | _       |               |

| 0FFA8H        | In-service priority register                    | ISPR         | R     | •                  | •       | _       |               |

| 0FFAAH        | Interrupt mode control register                 | IMC          | R/W   | •                  | •       | _       | 80H           |

| 0FFACH        | Interrupt mask register 0L                      | MK0L MK0     |       | •                  | •       | •       | FFFFH         |

| 0FFADH        | Interrupt mask register 0H                      | мкон         |       | •                  | •       |         |               |

| 0FFAEH        | Interrupt mask register 1L                      | MK1L         |       | •                  | •       | _       | FFH           |

| 0FFC0H        | Standby control register                        | STBC         |       | -                  | ●Note 2 | _       | 30H           |

| 0FFC2H        | Watchdog timer mode register                    | WDM          |       | -                  | ●Note 2 | _       | 00H           |

| 0FFC4H        | Memory expansion mode register                  | ММ           |       | •                  | •       | -       | 20H           |

| 0FFC5H        | Hold mode register                              | HLDM         |       | •                  | •       | _       | 00H           |

| 0FFC6H        | Clock output mode register                      | CLOM         |       | •                  | •       | _       |               |

| 0FFC7H        | Programmable wait control register 1            | PWC1         | ]     | _                  | •       | _       | AAH           |

| 0FFC8H        | Programmable wait control register 2            | PWC2         |       | _                  | _       | •       | AAAAH         |

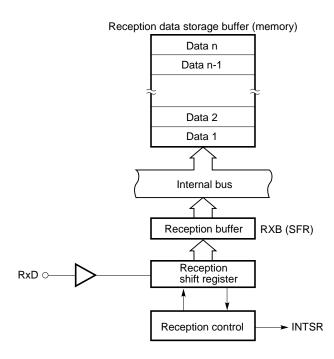

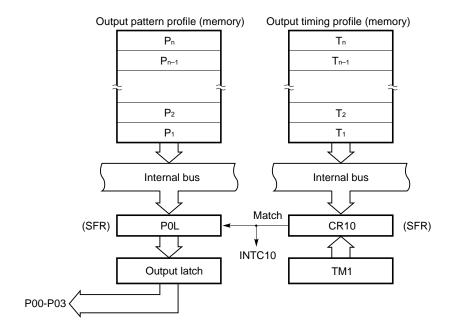

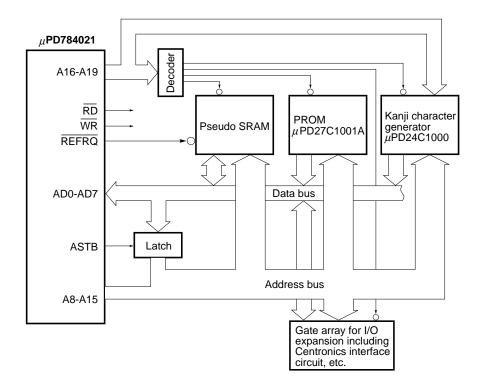

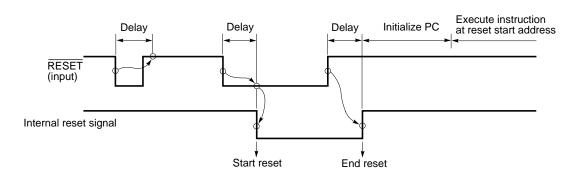

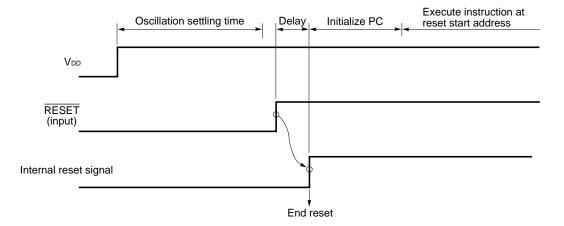

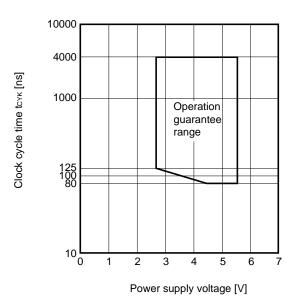

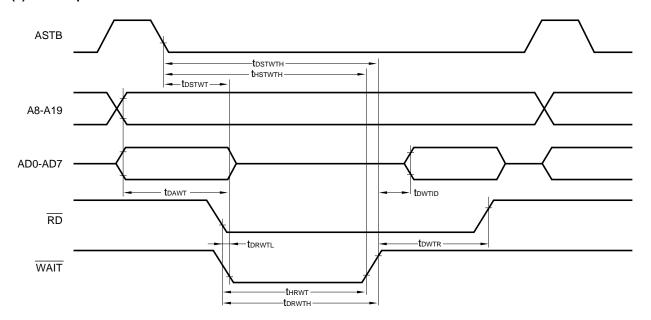

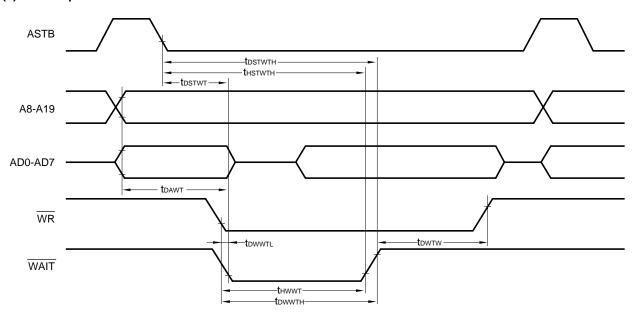

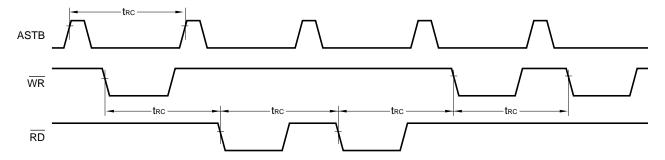

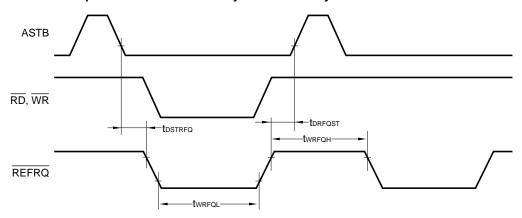

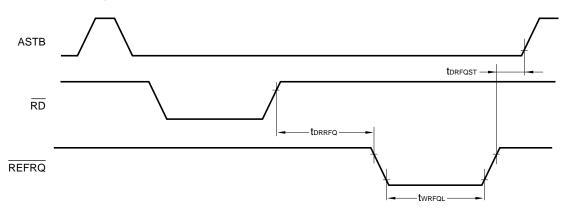

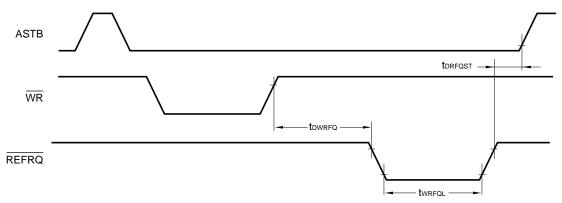

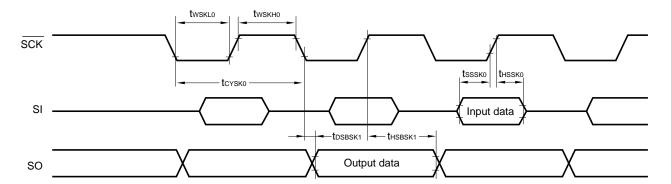

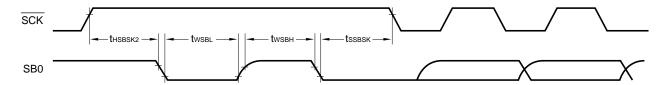

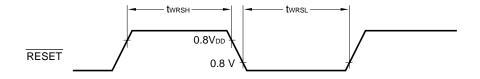

**Notes 1.** Applicable when the LOCATION 0 instruction is executed. When the LOCATION 0FH instruction is executed, F0000H is added to each address.