# DCR3650Y28

# **©2** ion implant

# **Phase Control Thyristor**

**Preliminary Information**

DS5875-1.2 September 2007 (LN25542)

## FEATURES

- Double Side Cooling

- High Surge Capability

# **APPLICATIONS**

- High Power Drives

- High Voltage Power Supplies

- Static Switches

### **VOLTAGE RATINGS**

| Part and<br>Ordering<br>Number         | Repetitive Peak<br>Voltages<br>V <sub>DRM</sub> and V <sub>RRM</sub><br>V | Conditions                                                                                                                                                                                                                                             |

|----------------------------------------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DCR3650Y28<br>DCR3650Y26<br>DCR3650Y24 | 2800<br>2600<br>2400                                                      | $ \begin{split} T_{vj} &= -40 ^\circ \!\! C \text{ to } 125 ^\circ \!\! C, \\ I_{ORM} &= I_{RRM} = 200 \text{mA}, \\ V_{DRM}, V_{RRM}  t_p &= 10 \text{ms}, \\ V_{DSM}  \&  V_{RSM} &= \\ V_{DRM}  \&  V_{RRM}  +  100 V \\ respectively \end{split} $ |

Lower voltage grades available.

### **ORDERING INFORMATION**

When ordering, select the required part number shown in the Voltage Ratings selection table.

For example:

#### DCR3650Y28

Note: Please use the complete part number when ordering and quote this number in any future correspondence relating to your order.

# KEY PARAMETERS

| V <sub>DRM</sub>   | 2800V    |

|--------------------|----------|

| I <sub>T(AV)</sub> | 3650A    |

| ITSM               | 50500A   |

| dV/dt*             | 1500V/μs |

| dl/dt              | 300A/μs  |

| dl/dt              | 300A/μs  |

#### \* Higher dV/dt selections available

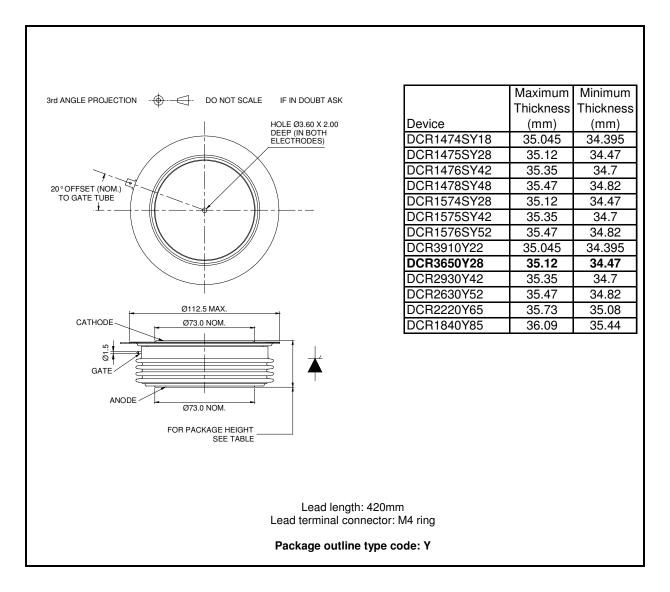

#### Fig. 1 Package outline

www.dynexsemi.com

## **CURRENT RATINGS**

$T_{case}$  = 60  $^{\circ}\!C$  unless stated otherwise

| Symbol              | Parameter                            | Test Conditions          | Max. | Units |

|---------------------|--------------------------------------|--------------------------|------|-------|

| Double Sid          | de Cooled                            |                          |      |       |

| I <sub>T(AV)</sub>  | Mean on-state current                | Half wave resistive load | 3650 | А     |

| I <sub>T(RMS)</sub> | RMS value                            | -                        | 5730 | А     |

| Ι <sub>Τ</sub>      | Continuous (direct) on-state current | -                        | 5105 | А     |

### SURGE RATINGS

| Symbol           | Parameter                               | Parameter Test Conditions                  |       |                   |  |

|------------------|-----------------------------------------|--------------------------------------------|-------|-------------------|--|

| I <sub>TSM</sub> | Surge (non-repetitive) on-state current | 10ms half sine, $T_{case} = 125 ^{\circ}C$ | 50.5  | kA                |  |

| l <sup>2</sup> t | I <sup>2</sup> t for fusing             | V <sub>R</sub> = 0                         | 12.74 | MA <sup>2</sup> s |  |

### THERMAL AND MECHANICAL RATINGS

| Symbol               | Parameter                             | Test Condition                  | Min.        | Max. | Units   |      |

|----------------------|---------------------------------------|---------------------------------|-------------|------|---------|------|

| R <sub>th(j-c)</sub> | Thermal resistance – junction to case | Double side cooled DC           |             | -    | 0.00835 | ℃/W  |

|                      |                                       | Single side cooled              | Anode DC    | -    | 0.0134  | °C/W |

|                      |                                       |                                 | Cathode DC  | -    | 0.023   | °C/W |

| R <sub>th(c-h)</sub> | Thermal resistance – case to heatsink | Clamping force 54kN Double side |             | -    | 0.002   | °C/W |

|                      |                                       | (with mounting compound)        | Single side | -    | 0.004   | °C/W |

| $T_{vj}$             | Virtual junction temperature          | On-state (conducting)           |             | -    | 135     | Ŝ    |

|                      |                                       | Reverse (blocking)              |             | -    | 125     | S    |

| T <sub>stg</sub>     | Storage temperature range             |                                 |             | -55  | 125     | °C   |

| Fm                   | Clamping force                        |                                 |             | 48.0 | 59.0    | kN   |

# **DYNAMIC CHARACTERISTICS**

| Symbol                             | Parameter                                     | Test Conditio                                                                            | Min.            | Max. | Units  |      |

|------------------------------------|-----------------------------------------------|------------------------------------------------------------------------------------------|-----------------|------|--------|------|

| I <sub>RRM</sub> /I <sub>DRM</sub> | Peak reverse and off-state current            | At V <sub>RRM</sub> /V <sub>DRM</sub> , T <sub>case</sub> = 125 °C                       | -               | 200  | mA     |      |

| dV/dt                              | Max. linear rate of rise of off-state voltage | To 67% V <sub>DRM</sub> , T <sub>j</sub> = 125℃, ga                                      | ate open        | -    | 1500   | V/µs |

| dl/dt                              | Rate of rise of on-state current              | From 67% $V_{\text{DRM}}$ to 2x $I_{\text{T}(\text{AV})}$                                | Repetitive 50Hz | -    | 150    | A/µs |

|                                    |                                               | Gate source 30V, 10Ω,                                                                    | Non-repetitive  | -    | 300    | A/µs |

|                                    |                                               | $t_r < 0.5 \mu s,  T_j = 125^\circ\!C$                                                   |                 |      |        |      |

| V <sub>T(TO)</sub>                 | Threshold voltage – Low level                 | 500A to 2500A at $T_{case} = 125$                                                        | 5°C             | -    | 0.8    | V    |

|                                    | Threshold voltage – High level                | 2500A to 7200A at $T_{case} = 12$                                                        | -               | 0.95 | V      |      |

| r⊤                                 | On-state slope resistance – Low level         | 500A to 2500A at T <sub>case</sub> = 125 ℃                                               |                 |      | 0.1714 | mΩ   |

|                                    | On-state slope resistance – High level        | 2500A to 7200A at T <sub>case</sub> = 125 ℃                                              |                 |      | 0.1114 | mΩ   |

| t <sub>gd</sub>                    | Delay time                                    | $V_D = 67\% V_{DRM}$ , gate source 30V, 10 $\Omega$                                      |                 | TBD  | TBD    | μs   |

|                                    |                                               | $t_r=0.5\mu s,T_j=25^\circ\!\!C$                                                         |                 |      |        |      |

| tq                                 | Turn-off time                                 | $T_j = 125 ^{\circ}C, V_R = 200V, dI/dt$                                                 | 100             | 250  | μs     |      |

|                                    |                                               | $dV_{DR}/dt = 20V/\mu s$ linear                                                          |                 |      |        |      |

| Qs                                 | Stored charge                                 | I <sub>T</sub> = 2000A, T <sub>j</sub> = 125 ℃, dl/dt                                    | 630             | 1800 | μC     |      |

| ΙL                                 | Latching current                              | $T_j = 25 ^{\circ}\text{C}, V_D = 5V$                                                    | -               | 3    | А      |      |

| Ι <sub>Η</sub>                     | Holding current                               | T <sub>j</sub> = 25 ℃, R <sub>G-K</sub> = ∞, I <sub>TM</sub> = 500A, I <sub>T</sub> = 5A |                 |      | 300    | mA   |

©2 forn Innplant

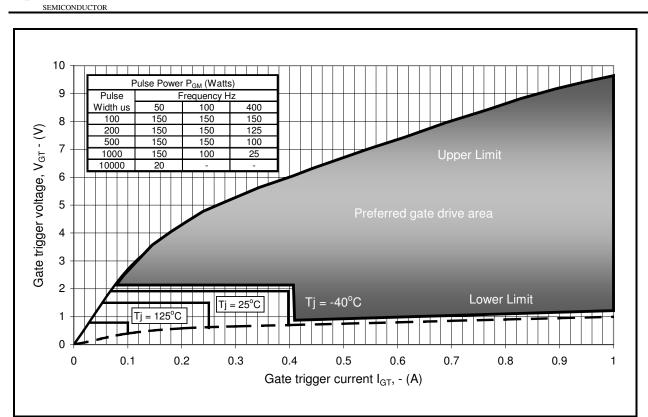

# GATE TRIGGER CHARACTERISTICS AND RATINGS

| Symbol          | Parameter                | Test Conditions                                 | Max. | Units |

|-----------------|--------------------------|-------------------------------------------------|------|-------|

| V <sub>GT</sub> | Gate trigger voltage     | $V_{DRM} = 5V, T_{case} = 25 ^{\circ}C$         | 1.5  | V     |

| $V_{GD}$        | Gate non-trigger voltage | At V <sub>DRM,</sub> T <sub>case</sub> = 125 °C | TBD  | V     |

| I <sub>GT</sub> | Gate trigger current     | V <sub>DRM</sub> = 5V, T <sub>case</sub> = 25℃  | 250  | mA    |

| I <sub>GD</sub> | Gate non-trigger current | V <sub>DRM</sub> = 5V, T <sub>case</sub> = 25℃  | TBD  | mA    |

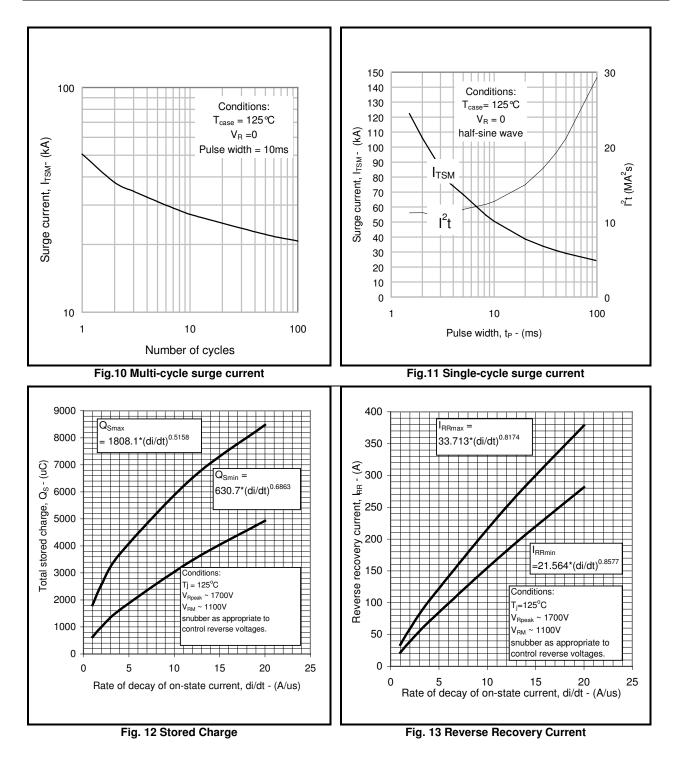

## **CURVES**

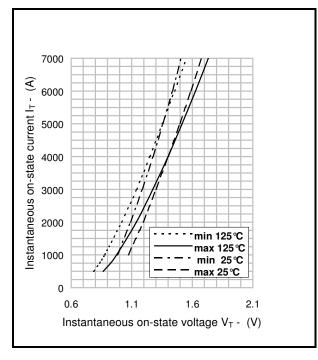

Fig.2 Maximum & minimum on-state characteristics

### **V<sub>TM</sub> EQUATION**

$V_{TM} = A + BIn (I_T) + C.I_T + D.\sqrt{I_T}$

Where A = 0.566974 B = 0.019159 C = 0.000059 D = 0.006897 these values are valid for  $T_j$  = 125 °C for  $I_T$  100A to 7200A

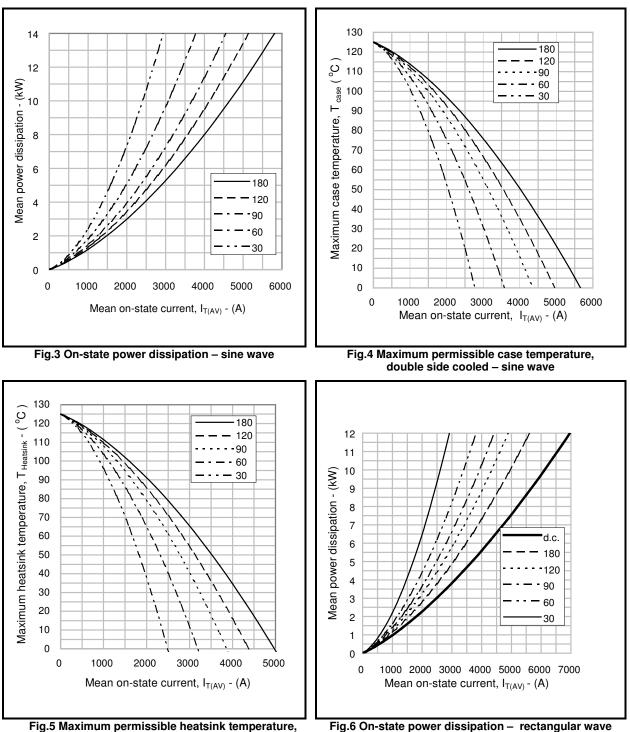

double side cooled - sine wave

@2 fort Implant

DCR3650Y28

6/10

10

5

0 0.001

0.01

0.1

1

Time (s)

10

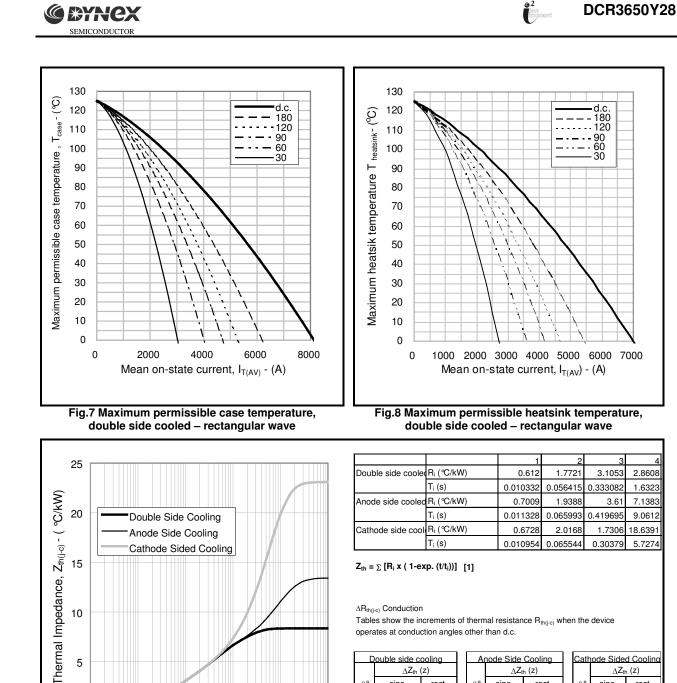

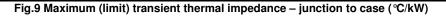

$\Delta R_{th(j\text{-}c)} \text{ Conduction}$ Tables show the increments of thermal resistance  $R_{th(j-c)}$  when the device

operates at conduction angles other than d.c.

| D   | ouble side cooling |                      |  | Double side cooling  |       |       | Anode Side Cooling |              |                  | Cathode Sided Cooling |  |  |  |

|-----|--------------------|----------------------|--|----------------------|-------|-------|--------------------|--------------|------------------|-----------------------|--|--|--|

|     | $\Delta Z_{th}$    | ∆Z <sub>th</sub> (z) |  | ∆Z <sub>th</sub> (z) |       |       |                    | $\Delta Z_t$ | <sub>h</sub> (z) |                       |  |  |  |

| θ°  | sine.              | rect.                |  | θ°                   | sine. | rect. |                    | θ°           | sine.            | rect.                 |  |  |  |

| 180 | 0.94               | 0.65                 |  | 180                  | 0.94  | 0.64  |                    | 180          | 0.94             | 0.64                  |  |  |  |

| 120 | 1.09               | 0.92                 |  | 120                  | 1.08  | 0.91  |                    | 120          | 1.08             | 0.91                  |  |  |  |

| 90  | 1.24               | 1.07                 |  | 90                   | 1.23  | 1.06  |                    | 90           | 1.24             | 1.06                  |  |  |  |

| 60  | 1.38               | 1.23                 |  | 60                   | 1.37  | 1.22  |                    | 60           | 1.37             | 1.22                  |  |  |  |

| 30  | 1.49               | 1.40                 |  | 30                   | 1.47  | 1.38  |                    | 30           | 1.48             | 1.39                  |  |  |  |

| 15  | 1.54               | 1.49                 |  | 15                   | 1.52  | 1.47  |                    | 15           | 1.53             | 1.48                  |  |  |  |

|     |                    |                      |  |                      |       |       |                    |              |                  |                       |  |  |  |

100

2.8608

1.6323

7.1383

9.0612

18.6391

5.7274

@2 fort Implant DCR3650Y28

©2 fori implant

DCR3650Y28

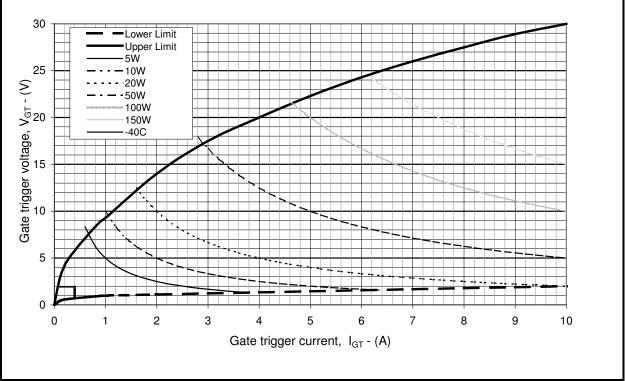

Fig14 Gate Characteristics

#### Fig. 15 Gate characteristics

@ BYNCX

©2 Innplant

## PACKAGE DETAILS

For further package information, please contact Customer Services. All dimensions in mm, unless stated otherwise. DO NOT SCALE.

Fig.16 Package outline

#### POWER ASSEMBLY CAPABILITY

The Power Assembly group was set up to provide a support service for those customers requiring more than the basic semiconductor, and has developed a flexible range of heatsink and clamping systems in line with advances in device voltages and current capability of our semiconductors.

We offer an extensive range of air and liquid cooled assemblies covering the full range of circuit designs in general use today. The Assembly group offers high quality engineering support dedicated to designing new units to satisfy the growing needs of our customers.

Using the latest CAD methods our team of design and applications engineers aim to provide the Power Assembly Complete Solution (PACs).

#### HEATSINKS

The Power Assembly group has its own proprietary range of extruded aluminium heatsinks which have been designed to optimise the performance of Dynex semiconductors. Data with respect to air natural, forced air and liquid cooling (with flow rates) is available on request.

For further information on device clamps, heatsinks and assemblies, please contact your nearest sales representative or Customer Services.

Stresses above those listed in this data sheet may cause permanent damage to the device. In extreme conditions, as with all semiconductors, this may include potentially hazardous rupture of the package. Appropriate safety precautions should always be followed.

http://www.dynexsemi.com

e-mail: power\_solutions@dynexsemi.com

HEADQUARTERS OPERATIONS **DYNEX SEMICONDUCTOR LTD** Doddington Road, Lincoln Lincolnshire, LN6 3LF. United Kingdom. Tel: +44(0)1522 500500 Fax: +44(0)1522 500550 CUSTOMER SERVICE Tel: +44(0)1522 502753 / 502901. Fax: +44(0)1522 500020

© Dynex Semiconductor 2003 TECHNICAL DOCUMENTATION – NOT FOR RESALE. PRODUCED IN UNITED KINGDOM.

This publication is issued to provide information only which (unless agreed by the Company in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information contrast nor to be repericted or service. Information contrast nor to be specification, design or price of any product or service. Information contending possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to the Company's conditions of sale, which are available on request.

All brand names and product names used in this publication are trademarks, registered trademarks or trade names of their respective owners.